반도체에 관해서 궁금한 것이 있으면 www.semipark.co.kr에 가시면 됩니다.

웨이퍼 제조 회사

LG-Siltron , SUMCO, SUMITOMO, MEMC, SHINITSU

반도체 회사들은 주로 위의 회사에서 만든 웨이퍼를 많이 씁니다.

Fabrication(FAB)

일반적으로 반도체 회사를 말한다면 FAB을 말하는 것입니다. 전체 반도체 공정에서 가장 긴 시간이 소요되며, 가장 많은 설비 투자가 필요한

곳입니다. FAB도 여러가지로 나눌수가 있는데 인텔이나 삼성, 하이닉스 마이크론, 인피니온, 르네사스, TI, ST-Micro 같은 회사들은

자체의 설계와 공정을 이용해서 자기의 제품을 만드는 회사들이고 TSMC, UMC, SMIC, 동부아남 같은 회사들은 설계를 가지고 있지 않지만

자체의 공정을 가지고 있어서 FAB-less 회사들의 주문을 받아 반도체를 생산합니다. 이런 부류의 회사를 Foundary라고 합니다. 대부분의

FAB들은 TEST까지 겸하고 있습니다. 전세계적으로 FAB들이 수시군데가 넘는데 일일히 나열하기는 힘들것 같군요.

Package

큰 회사의 경우에는 Package까지도 같이 하고 있습니다. Package만 전문으로 하는 회사로는 우리나라의 AMKOR(예전의

아남반도체), STECO(삼성자회사)가 유명합니다. Package 회사도 상당히 많은 것으로 아는데 저의 한게는 여기까지입니다.

장비업체

Photo : ASML, CANON, NIKON

ETCH : AMT(Aplied Material), TEL

기타 : NOVELUS, AMAT, SEZ, KLA TENKOR, ........

웨이퍼 제조회사

LG-Siltron , SUMCO , SUMITOMO , MEMC , SHINITSU

Fabrication (FAB)

IDM(일괄공정)

인텔,삼성,하이닉스,마이크론,인피니온,르네사스,TI,STmicro

Foundry

TSMC,UMC,SMIC,동부아남

Package

AMKOR,STECO

반도체 공정별 장비·재료

|

공정별 장비·재료

◇ Equipment by Unit Process |

| ◎ Lithography |

| ♠ Photomasks/Mask Aligner |

♠ Mask/Reticle Manufacturing

Equipment |

| ♠ Photoresist Processing |

♠ Photoresists |

| ♠ Positioning Equipment |

♠ Wafer Steppers & Scanners |

| ◎ Thermal Processing

/Implant |

| ♠ Thermal: Annealing, RTP, Laser, E-Beam |

♠ Furnaces/Diffusion/Oxidation Equipment |

| ♠ Ion Implanters |

| ◎ Deposition |

| ♠ Chemical Vapor Deposition Equipment(LPCVD,

PECVD) |

| ♠ Sputtering(PVD)/Electroplating |

| ◎

Etching/Planarization |

| ♠ CMP Equipment |

♠ Plasma Etch |

| ♠ Wet Chemical Processing |

|

| ◎

Packaging/Assembly |

| ♠ Bonding: Wire, Die, TAB |

♠ Dicing, Scribing and Die Separation |

| ♠ Packaging, Encapsulating, Sealing |

|

| ◎ Test/Metrology

/Inspection |

| ♠ Defect Inspection/Failure Analysis |

♠ In-situ and In-line Monitoring |

| ♠ Measurement Systems |

♠ Microscopes: Optica |

| ♠ Microscopes: Non-optical |

♠ Patterned Wafer Inspection/CD Measurement |

| ♠ Testers(Parametric and Functional)/Probes |

|

| ◎ Contamination Control Vacuum

equipment |

| ♠ Contamination Control Products |

♠ Static/Vibration Control Equipment |

| ♠ Vacuum Pumps |

♠ Residual Gas Analyzers |

| ♠ Vacuum components(Bellows, Chambers, Gauges,

Valves, etc.) |

| ◎ Automation/Wafer

Handling |

| ♠ Interbay/Interbay Automation |

♠ Robotics |

| ♠ Wafer Cassettes, Boats |

♠ Diagnostics Software |

| ♠ Fab Automation Software |

♠ Yield Management Software |

| ♠ Advanced Compoment |

♠ Equipment |

| ♠ LCD |

♠ Accesarils | |

| ◇ Materials by

Process |

| ◎ Chemicals &

Handling |

| ♠ Chemicals |

♠ Chemical Delivery |

| ♠ Thin Film Materials |

♠ Wafer/Substrates |

| ♠ Materials(FEOL/BEOL) |

|

| ◎ Gases/Gas

Handling |

| ♠ Gases |

♠ Mass Flow Controllers |

| ♠ Gas Filters/Cabinets/Panels |

|

| ◎ Function

Materials |

| 실리콘 웨이퍼, 화합물 웨이퍼 |

| ◎ Process Materials |

| Photomask(Reticle, Working Mask),

Photoresist(Positive, Negative) Chemical(Process, Diffusion), Gases(Specialty,

분위기), Metal(Al, Ti, W, 합금) |

| ◎ Packaging

Materials |

| Lead Frame(Stamped, Etched), Bonding Wire(Au,

Al)Packaging(EMC, Ceramic, Adhesive) |

| ※ 세정용 Wet Chemical & Gases

| |

추가!

반도체 장비/공정 기술 용어집

1. 기본 공통 용어

(영어 사전상의 의미보다는 반도체 공정에서 일반적으로 사용되는 용어

입니다.)

용어 한글 표기 용어의 의미

Abort 중지 Processs 진행중 장비 이상등으로 인해Process

를 중지시키는 것

Agent 대리인 "외국장비 Maker 대신으로 장비를 Set-up문제조치 및

유지등을 지원하는 사람"

Adjust 조정 "장비또는 Controller등에서 기계적 또는 전기적으로 어떤

이상

적인 값이나 상태를 만들기 위해 조정해

주는것"

Align 정렬 "장비 또는 어떤 물질을 기계적, 물리적으로 정렬시켜 기본적 상태로 만들어 주는

것."

Air shower 공기 샤워 "Fab 內 청정도를 유지하기 위해 P/T 감소 방법으로 Class가

낮은

곳에서 높은 곳으로 이동할 경우 Air힘으로 P/T를 제거시키는

것"

Accuracy 정돈, 정확도 "동작한 물체의 정도가 얼마만큼 정확하게 움직였는지 또는

얼마

만큼 정확한 값이 나타내는

용어"

Axis 축 기계 상에서 회전부의 중심부분을 의미함

B.M(Breakdown

Maintenonce) 비, 엠 장비에 문제또는 고장이 발생한후 취해지는 조치및

수리

Bake 베이크 "PR 등에 포함되어 있는 습기를 없애기 위해 고온으로 Wafer등을 처리하는 것

"

Ball Valve 볼 밸브 "Pump Exhamst부에 Pump로의 Back stream을 방지하기

위해

Valve 내부에 고무형태의 Ball이 들어있는

Valve"

Batch 배치 단위 Process중 동시에 여러장의 Wafer 를 처리하는

형태

Bay 베이 Fab 을 공정별로 구분하여 지정한

Area

Bearing 베어링 "동력전달부에 마찰을 줄이고 원활한 동력을 전달하기 위해 설치 되는

부품"

Bipolar 바이폴라 "Unipolar와는 대조되는 의미로서 전하는 이동하는

Carrier를

Electron과 hole이 동시에 역할을 담당하는

것"

Bit 비트 Memory의

기본단위(1Byte=8bits)

Booster 부스터 "보통 Booster pump를 말하며 pump

speed를 증가 시키기 위해

보조 Pump로 사용(단독

사용불가)"

Bottle Neck 병목현상 "장비의 생산처리 능력 부족및 백업장비 부재로 인해

Wafer(Run)

가 밀집되는

현상"

Calibration 측정 장비 사용중 Reference값의 변화를 바로 잡는

것

Capa 캐파 Capability의 준말로

Wafer처리능력

Capacitor 캐패시터 전하를 저장할수 있는

소자

Carrier 캐리어 "① Wafer 를 이동시 사용하는 플라스틱

용기

② 반도체에서 전하를 이동하는

입자"

Cassette 카세트 Wafer 끼리 접촉을 막기위해 Slot를 만들어 놓은 Wafer

보관용기

Chamber 캠버 Process가 진행되는 밀페된

공간

Chiller 냉동기 Cooling Water의 온도를 조절하는

장치

Chip 칩 "Wafer 제조공장에서 완성된 제품의 한조각을 말하며 한장의 Wafer에는 수많은

Chip이

형성되어 있다"

Clamp 클램프 Process중wafer를 고정시키는

장치

Clean Mat 무진매트 "Clean Room용 신발바닥에 묻은 Particl을 제거하기 위해

만든

접착력이 있는 매트"

Clean

Note 무진노트 Fab內에서 사용되는 Particle이 발생되지 않는 종이로 만든 Note

Clean

Room 청정실 "Particle 발생을 억제하고 Filter를 이용하여 발생된 P/T을

제거하여

먼지가 거의 없는

공간"

Collector 콜렉터 Tr에서 전자를 받아 들이는

부분

Compressor 냉동기 "Cryo pump 에 압축 He을 보내 Cryo pump 內의 온도를

낮추는 장치"

Crack 크랙 "SOG 공정등에서 OCD 용액이 굳으면서 수축되어 일어나는

부스러기"

CVD 화확적 기상증착 Chemical Vapor Deposition의 약자로

Deposition할 물질을 고온으로 증발

시켜 wafer에 증착되도록 하는 Thin Film 성장

방법

CD 시디 "Critical Dimension의 약자로 Photo공정에서 Reticle의 패턴을

웨이 퍼에 노광후

현상시킨후의 선또는 패턴의 폭 또는 길이를

의미함."

Deposition 증착 물질을 Wafer 표면에 쌓이도록 하는

것

Develop 현상 PR이 도포된 웨이퍼를 노광장비에서 노광후 현상하는

과정

Diffusion 확산 Doping 된 불순물을 주변으로 퍼지게 하는 과정

Dry

Etch 건식각 "Chemical을 사용하지 않고 Plasma를 이용하여 불필요한 부분을 없애는

것"

Dummy wafer 더미 웨이퍼 "생산 Wafer의 빈자리를 매워 Batch 단위의 공정이

진행될수

있도록 사용하는

Wafer"

Edge 에지 Wafer의 Device가 없는 가장자리 부분

Ellipso

Meter 엘립소 메타 Oxide 두께를 측정하는 장치

Emergency 비상 문제발생시

긴급하게 장치의 Power를 차단

Emitter 에미터 Tr 에서 전자를 방출하는

부분

Etch 식각 필요한 부분을 제외한 나머지 부분을 깍아 없애는 것

Etch

Rate 식각정도 식각되는 속도의 정도

FAB 팹 Fabrication의 약자로 Si웨이퍼가

가공되는 곳

Four Point Probe 포 포인트 프로브 Wafer표면 저항을 측정하는

장치

Furnace 로 Oxide 및 Anneal작업을 하는

로

Gate 게이트 FET에서 Source에서 Drain으로 가는 Electron의 양을 조절하는

부분

Gate Oxide 게이트 옥사이드 Gate를 보호하기 위한

산화막

Grinder 그라인드 Wafer의 뒷면을 가공하는 장치(back

grinder)

G Line G선 "Mercury Lamp에서 나오는 약 200nm~700nm대역의 파장중

436nm

파장의 빛을 말하며 노광원으로 사용된다"

Hole 정공 +

전하를 띠고 Electron과 같이 전하를 이동하는 입자

I Line i선 "수은 램프에서 나오는

보통200nm~700nm의 파장의 빛중 i선에 상당하는

365nm대의 파장"

Ion 이온 원자나 분자가 전하를 띤

상태

Ion Gauge 이온게이지 "분자나 원자를 이온화시켜 그내부의 입자수를

Check하는Vacuum

Gauge 일종"

Ion

Implantation 이온주입 Wafer에 불순물을 주입하는 공정

LoT 로트 Wafer의

공정 수량 단위

Mano Meter 마노메타 배기부의 압력을 측정하는 계기

Metal

Contamination 금속오염 "장비를 구성하고 있는 금속의 부분이 Sputtering되어 Wafer에

증착되어 Device에 나쁜 영향을

준다"

Metal Etch 메탈식각 Metal Line외의 부분을 깍아내는

공정

MFC 엠에프시 Mass Flow Control의 약자로 유체의 흐름을 조절하는

장치

MOS 모스 "Metal Oxide Semiconductor의 약자로 반도체(Si)의 표면에 산하막

(SiO2)을 형성하고

그위에 금속을 붙인 구조를 가지고 있다."

Marker 마커 "웨이퍼의

플랫존 부분에 LOT 이름 및 웨이퍼 번호등 을 만들어 주는장비"

O-Ring 오링 Vacuum

Sealing 부분에 사용되는 고무재질의 링

Oxidation 산화 Si와 O2가 결합하여 SiO2가 되는

것

Oxide 산화막 절연및 Device 보호를 위한 산화막

Oxide Etch 산화막

식각 Ion주입을 위해 산화막의 일부를 제거하는 것

PR 피알 Photo Resistor의

약자로 일종의 감광액

Pattern 패턴 Mask에 Design된 Device의

형태

Photo 포토 "식각부위나 이온주위 부분을 지정하기 위해 일정부위를 보호하기 위한

Mask작업을

하는 공정"

PR Strip 피알제거 Photo Resistor를

현상액으로 약하게 한다음 Chemical로 제거하는 것

Quartz 석영 단결정의 수정을 가공해서 만든

무오염의 Wafer 취급 Part

Scrubber 스크러바 Toxic물질을 중화시키거나 걸러내는

장치

SEM 샘 "Scanning Electron Microscope의 약자로 주사형 전자현미경을

말함

시료의 표면을 전자빔에 의해 텔레비전식으로 주사하고 거기에서

나오는 2차 전자,

반사전자또는 시료전자를 검출하여 관찰하는 장치"

Signal Tower 시그날 타워 장비의 상태를

알려주는 Tower Lamp

Silicon 실리콘 Si, 4가 원소로서 반도체의

주원료

SOG 에스오지 Spin On Grass의 약자로써 Wafer의 평탄화로 Topology를 좋게

한다

Spec 스펙 공정에서 지정한 규정 또는 기준

TAT 티에이

티 Turn Around Time의 약자로 Wafer투입후 가공완료까지의

소요시간

Thereshold 문턱 Tr이 동작되기 위한 최소한의

Voltage

Throughput 생산성 단위 시간당 처리할수 있는

능력

Tilt 틸트 Channel 현상을 방지하기 위해 Wafer에 각도를 주는

것

Tweezer 튀져 Wafer handing

도구

Tube 튜브 Furnace 공정이 진행될수 있도록 Quartz로 만든

용기

Ultra Sonic Cleaner 초음파 세척기 초음파를 이용한 Cleaning

도구

Utility 유틸리티 장비 운전에 사용되는 전기, 물, 공기따위의

재료

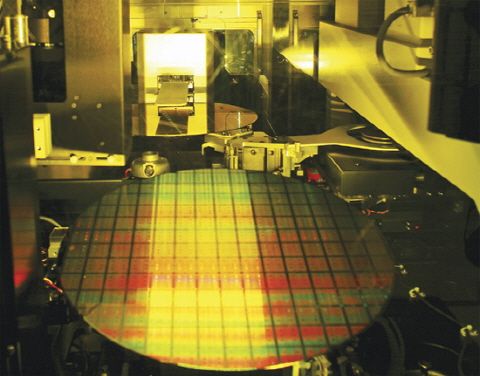

Wafer 웨이퍼 Chip을 만들기 위해 Si로 만들어진 판

Wet

Etch 습식각 Chemical를 이용한 식각 방법

Wet

Station 윁스테이션 습식각이 진행되는 장소

Yield 일드 투입한 Input량의 비율을

계산하여 산출량을 나타낼때 사용

Fab Yield (생산일드)

Probe Yield

(Test 일드)

PKG Yield (패키지 일드)

F/T Yield(Final

Test일드)

전공정 후공정 !!!

전공정은 웨이퍼위에 회로를 만드는 과정이라고 보시면 되고요 후공정은 기판위에 만들어진 회로들을

하나하나씩 짜르고 외부와 접속할 선을 연결하고 패키지하는 과정입니다. 자세한 내용은 밑을 참고하세요.

<대분류>

회로설계

⇒ 패턴설계 ⇒ 마스크제작 ⇒ 웨이퍼 프로세스(전공정),기판공정(FEOL) ⇒

Si다결정제조 ⇒ Si단결정제조 ⇒ 경면 Si웨이퍼제조

↗

⇒ 배선공정(BEOL) ⇒ 조립공정(후공정) ⇒ 검사공정(후공정) ⇒ 신뢰성검사공정(후공정) ⇒

제품출하

<소분류> - 전공정 웨이퍼 프로세스

1. 기판공정(FEOL)

- 에피택시얼층 형성 ⇒

아이솔레이션(트렌치.LOCOS) ⇒ 웰 형성(n웰.p웰) ⇒ 게이트산화막 ⇒

게이트전극형성 ⇒ 스페이서형성 ⇒ 커패시터 구조형성(DRAM)

⇒ 소스드레인형성 ⇒

배선 전 층간 절연막형성 ⇒ 평탄화공정 ⇒ 콘택트 홀 형성 ⇒ 콘택트 플러그형성

위의 공정이 끝난

후

2. 배선공정(BEOL)

- 콘택트 형성 ⇒ 배선패턴 형성(베리어층,메탈층,방사방지막) ⇒ 층간 절연막형성 ⇒ 평탄화공정

⇒

비어 홀 형성 ⇒ 비어 플러그 형성 ⇒ 배선패턴 형성(베리어층,메탈층,방사방지막) ⇒

<반복공정> ⇒

패시베이션

<기본 프로세스 기술의 분류>

- 대분류 - - 중<소>분류

-

1. 세정공정 ⇒ 웨트세정, 드라이 세정 등...

2. 열처리공정 ⇒ RTP(래피드 서멀)산화, 노(퍼니스)산화, 각종 어닐처리

등...

3. 불순물도입공정 ⇒ 이온 주입법, 열확산법, 이온도핑법 등...

4. 박막 형성공정 ⇒ 에피택시얼성장,CVD(화학적

기상성장),PVD(물리적 기상성장),도포막(SOG),도금법.

5. 리소그래피공정 ⇒ 레지스트 처리 ---- 레지스트도포, 베이크, 현상,

큐어, 레지스트제거.

패턴 에칭 ---- 드라이에칭, 웨트에칭.

노광기술 ---- 자외선, 전자빔, X선 등...

6. 평탄화

공정 ⇒ CMP(화학적 기계연마), 에치백 등...

★ 기본 프로세스 기술의 설명

1. 세정기술 (Cleaning)

-

세정은 리소그래피를 처음으로 하는 각 공정 사이에서 반드시 행해야 하는 것으로, 표면 청정화를

위한 공정이다. 또한 열처리,산화 등의

공정전에 행하여지는 것으로 "후처리","전처리"라 불리기도

한다. 이공정은 여전히 약액을 사용하는 웨트처리가 중심으로 ,RCA 세정의

경우는 H2SO4,HCI,NH4OH,

HF,H2O2 등의 약액 조합에의해 처리된다.

2. 열처리 (Thermal

Treatment)

- 보통, 실리콘 기판을 800℃ 이상의 고온 산화 분위기 속에서 처리하면 표면에 실리콘 자체의

산화막

(SiO2)이 형성된다.

이막은 절연막으로써 실리콘을 사용하는 반도체 디바이스 제조의 출발점이다. 실리콘

플레이너

(Planar)방식의 기본이며, MOS 구조에 있어서는 게이트 절연막이 된다.

이들 산화막이 형성에는 청정한 분위기의

확산로가 쓰여지며, 철저하게 세정을 실시한 웨이퍼가 사용된다.

3. 불순물 도입 (Impurity Doping)

- 불순물

도입이란, Si 기판중에 B, As, P 등의 Ⅲ 가 및 V 가 족 원소를 불순물로서 도입, pn접합 형성과 불순물 농도제어를 행하는

기술이다.

열적인 확산법과 이온주입법이 있는데 현재로써는 이온주입법이 주류를 이루고 있다.

이온주입법에서는, 진공 상태에서 분리되어진

B, As, P 등의 이온에 고전압을 가해 가속시킴으로써 기판안에 주입안다.

불순물의 양은 이온전류에 의해 모니터 되고 열처리에 의해

활성화된다.

4. 박막 형성 (Thin Film Deposition)

- 기판상에 절연막, 실리콘막, 금속막을

형성(퇴적)시키는 막으로 CVD(Chemical Vapor Deposition :화학적 기상성장) 및

PVD(Physical Vapor

Deposition :물리적 기상 성장)가 분리되어 사용되고 있다. SiO2, PSG, BPSG Si3N4 등의 절연막, 폴리실리콘막 및 W

등의 금속막은 CVD법에, A1, TiN 등의 금속 또는 도전성 막은 PVD법인 스퍼터링(Sputtering)에 의해 형성된다.

그외의

박막형성법으로는 회전 도포에 의한 코팅, 졸겔법이라고 불리는 절연막 형성법이 있다.

5. 리소그래피 기술 (Lithography)

- 리소그래피는 포토레지스트를 도포하는 공정으로 시작해 노광, 현상,

에칭, 포토레지스트 제거에 이르는 일련의 프로세스이다.

현상까지를 레지스트 처리공정으로 하며, 에칭 공정과 분리해서 생각할 수도

있다.

현재, 패턴 노광은 레이클이라 불리는 마스크 기판에 의해 축소 투영 전사시킴으로써 행해지고 있다. 이 공정은 모든 프로세스 기술의

중심이며, 반도체 공장에서도 가장 많은 금액의 투자를 필요로 하는 장치이다.

패턴 형성 후에는 반드시 에칭 공정이 수반되며 현성된

포토레지스트 패턴을 마스크로 하여 처리할 수 있다.

6. 평탄화 기술 (Planarization)

- 이 기술은, 최근에 와서

새롭게 사용되는 가공기술의 하나라 해도 좋을 것이다.

디바이스의 미세화와 고밀도화가 진행되면서 표면의 구조가 복잡, 요철이 심화되어지고,

특히 다층 배선공정에 있어서 단선이나 쇼트의 원인이 되기가 쉽다.

평탄화 기술은 그러항 이유 때문에 필요로 하게 되며 앞서 언급한 CMP

기술이 그 요체이다.

스태퍼에서 패턴을 투영할 때, 그 초점 심도의 감소에 대응하기 위해 표면을 평탄화하는 것도 필요한데, 항상 평탄한

면에 축소 투영을 실행함으로써 해상도를 높이는 효과가 크다.

평탄화에는 CMP법 이외에 에치백법과 플로(Flow)에 의한 평탄화법도

이용되고 있다. 또 패턴 형성을 위한 드라이에칭이 곤란한 Cu의 얇은 막 등에는 CMP법을 응용한 절연막 홈 내에 박아넣는

다마신(Damascene)법이 이용된다.

제조공정 전공정, 후공정...

일단 제가 알고 있는 반도체 제조 공정에 대해

답변하겠습니다.

전공정은 저도 잘 알고 있지 못해서....

일단 웨이퍼(반도체)가 만들어지면 이것을 하나의 상품으로 만드는 과정을

후공정이라고 합니다. TCP공정을 예를 들어서 설명하겠습니다

이런 웨이퍼을 제조회사에서 사들여서.......

수입 검사부터 하겠죠.

대부분이 샘플링 개념으로 수입 검사을 하고 있습니다.

이런 웨이퍼을 상품으로 만들기 위해 웨이퍼 하나씩 잘라야 합니다. 이 때 웨이퍼을

고정하기 위해서 tape에 웨이퍼을 붙입니다. 이 공정을 웨이퍼 마운틴이라고 합니다. 자른기 위한 준비가 다 되었으니까 웨이퍼을 자릅니다. 이

공정을 sawing공정(소잉공정)이라고 합니다. (동글란 웨이퍼상태에서 네모난 칩 하나씩 자른는 공정) 자른 칩을 상품화 시킨기 위해 본딩이라는

공정을 합니다. 이 본딩의 공정은 칩과 리드을 붙이는 공정입니다.

이 공정이 끝나면 칩과 리드을 보호하는 차원에서 칩 위에 수지을 덮어

씌웁니다. 이 공정을 pot공정이라고 합니다. 그리고 이런 pot공정이 끝나고 수지을 말리기 위해 오븐에 제품을 넣고 수지을 말립니다. 이

작업을 공정이라는 표현을 사용하지 않습니다. 제품에 제조회사에서 관리하는 일련번호을 인쇄하는 마킹공정이 있습니다. 그 다음은 검사 공정입니다.

이 검사 공정은 외관검사, Final test(전기적 특성검사)가 있습니다. 외관 검사는 말 그대로 현미경을 통해 제품을 보고 외관이 불량한

것을 가려내는 것입니다. Final test도 제품에 전기을 인가하여 제대로 동작하는지 가려내는 것입니다. 그리고 나서 packing공정입니다.

packing공정은 말 그대로 제품을 포장하는 공정입니다.

In a presentation entitled "

In a presentation entitled "

반도체장비회사리스트 포함.pdf

반도체장비회사리스트 포함.pdf

Pingback: Blog Review October 14 2013 | Solid State Technology

Pingback: Blog Review October 14 2013 | Semiconductor Manufacturing & Design Community

Pingback: Intel stands firm on 450mm; challenged by defects at 14nm | Pete's Posts Blog

Due to the delay of Intel’s 14nm FinFET manufacturing to the first quarter of 2014, TSMC’s first 16nm FinFET will be the most advanced process technology to be manufactured below Intel’s 22nm node in the 4th quarter of 2013. The device electrical transfer characteristics to be presented at the IEDM look impressive, and will be very interesting if Intel’s 14nm FinFET data could be published for a comparison.